iverilogを用いた論理回路シミュレーション¶

目的¶

例えば、論理回路のみを用いたロジックの検証などを手動で行うのは、とても大変。 そのため、PC上でそれを確認し、かつ、各組み合わせを視覚的に表現するために、 iverilogを用いる。

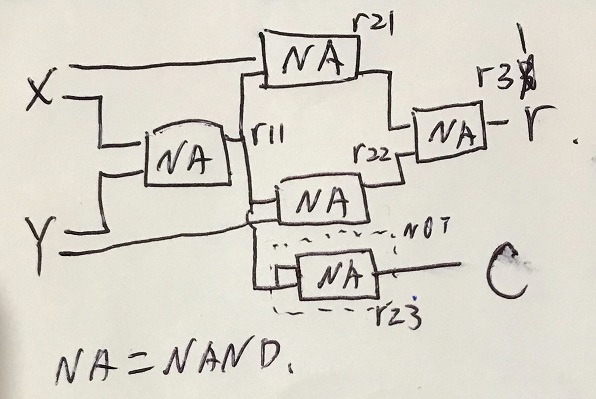

今回の対象は以下の図。半加算器であり、x,yがinputでrがsum, cがキャリー。

コード¶

module HA( input x, y, output r, c);

logic r11, r21, r22, r23, r31;

assign r11 = x ~& y;

assign r21 = x ~& r11;

assign r22 = y ~& r11;

assign c = r11 ~& r11;

assign r = r21 ~& r22;

endmodule

module test;

logic a, b, c, s;

HA adder(.x(a), .y(b), .r(s), .c(c));

initial begin

$dumpfile("test.vcd");

$dumpvars(0, test);

$display("A B C S");

$monitor("%b %b %b %b", a, b, c, s);

a = 0; b = 0; #1;

a = 0; b = 1; #1;

a = 1; b = 0; #1;

a = 1; b = 1; #1;

$finish;

end

endmodule

iverilog -g2012 -o test test.v

vvp test

VCD info: dumpfile test.vcd opened for output.

A B C S

0 0 0 0

0 1 0 1

1 0 0 1

1 1 1 0

可視化¶

上記でvcdファイルが生成されるので、/mnt/dなど、windowsからアクセスできるところに置く。 次に、gtkwave d:\test.vcdなどと実行し、 右上のウィンドウからtestの”+”などを掘り下げ、

viewのshow field high valueをチェックすると見やすい。